|

|

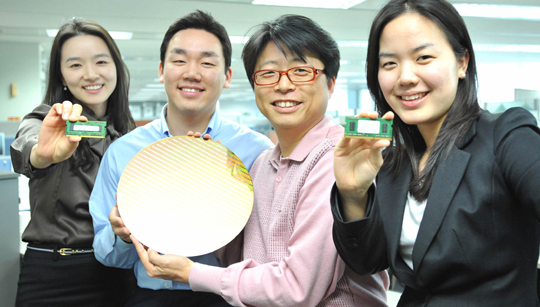

世界最大メモリー半導体企業の三星電子が回路幅30ナノメートルの生産工程でDRAMを製造するのに初めて成功した。同社は先月、半導体素子に入る回路の線幅が30ナノの工程で2Gb(ギガビット)DDR3 DRAMを作り出す技術開発に成功したと1日、明らかにした。下半期から量産に入る計画だ。

三星電子は00年に150ナノ工程技術を出して以来10年間、9回にわたり同分野で‘世界初’記録を継続している。三星電子は昨年1月、40ナノ級DRAMを開発し、その後30ナノ級工程に移った。50ナノ級工程から40ナノ級工程まで2年4カ月かかったが、今回はアップグレードの速度が上がったということだ。三星電子は昨年7月から生産ラインで40ナノ工程でDRAMを量産している。

同社は報道資料で「その間、DRAMのセル構造上、現在の生産工程では40ナノ級DRAMが技術的な限界と見なされたが、1年でこれを克服した」と明らかにした。

三星電子は30ナノ工程技術を前面に出しながら、競争企業との技術格差をさらに広げるという戦略だ。世界メモリー業界のうちハイニックス半導体だけが昨年11月から40ナノ工程でDRAMを量産している。日本と台湾の企業は50-60ナノ水準にとどまっている。ハイニックスも年末までに30ナノ工程の開発を終え、来年中に量産体制に入るという目標だ。

三星電子メモリー担当の趙秀仁(チョ・スイン)社長は「30ナノ級の製品開発に成功したことで、競争会社との格差を1年以上に広げた。30ナノ級DRAMは最高性能の親環境ソリューションを提供する製品で、これを前面に出してDRAM市場シェアを高めていきたい」と述べた。

微細工程の開発は20ナノにつながる見込みだ。物理学界では現実的に10ナノ工程まで可能と考えられている。10ナノより細くなる場合、シリコンではなく他の素材をメモリー用として使用する必要があるという見方が多い。

この記事を読んで…